http://sites.schaltungen.at/elektronik/home/basteln/pcb-service/leiterplatten-designWels, am 2016-03-13BITTE nützen Sie doch rechts OBEN das Suchfeld [ ] [ Diese Site durchsuchen]DIN A3 oder DIN A4 quer ausdrucken ********************************************************************************************* DIN A4 ausdrucken (Heftrand 15mm / 5mm)

****************************************************************

Leiterplatten-Lexikon

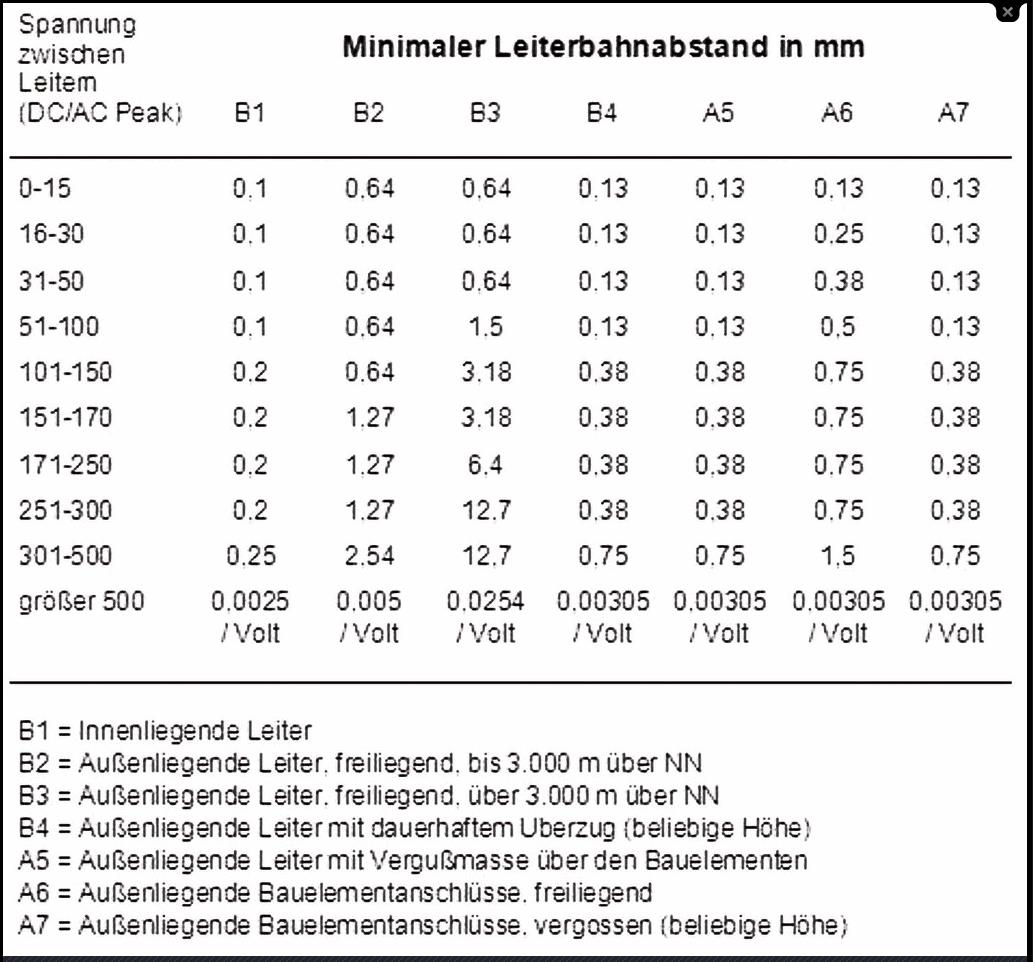

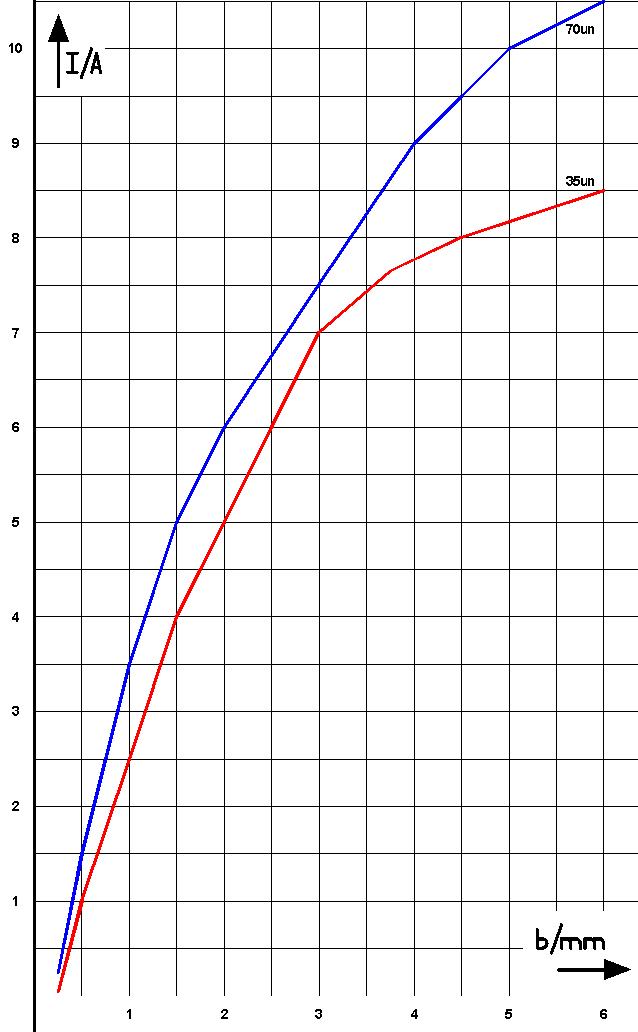

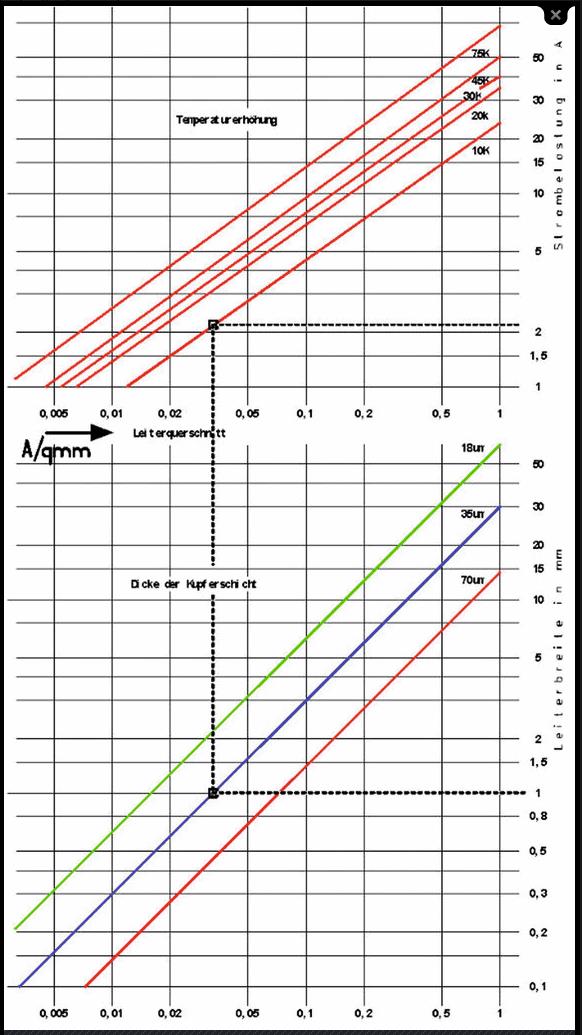

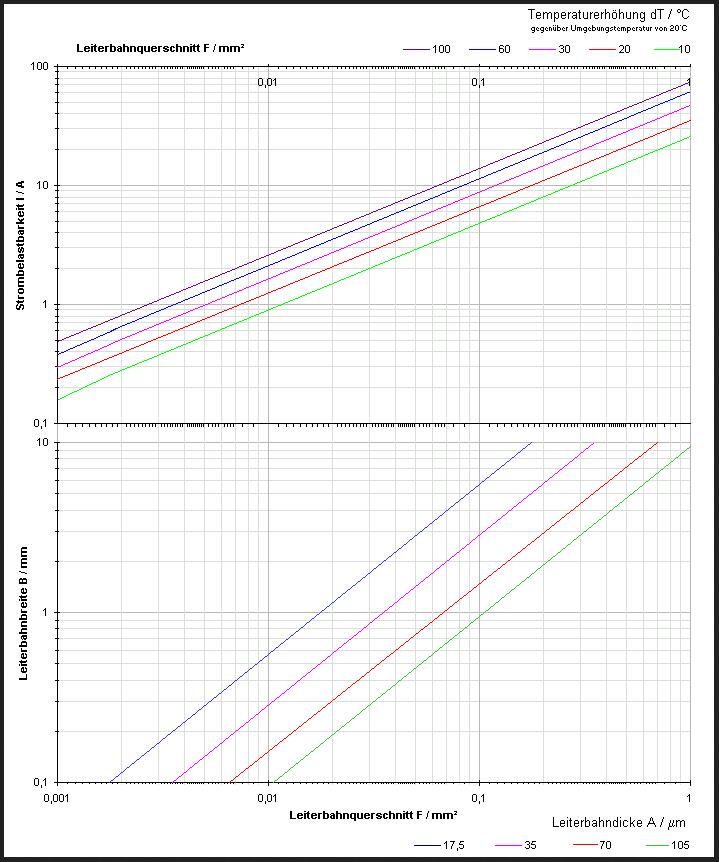

Leiterplatten-Layout / Layout einer Leiterplatte Layout-Systeme Bauteil-Liste / Netzliste / Stromlaufplan der Schaltung PCB-Designer Leiterplatten-Herstellung DRC = Design-Rule-Checks Leiterbahnabstand / Leiterbahnbreite Leiterabstand / Leiterbreite EDA-Tool http://www.andus.de/support/leiterplatten-lexikon.php http://www.andus.de/service-download/download.php

PCB-Design-Regeln

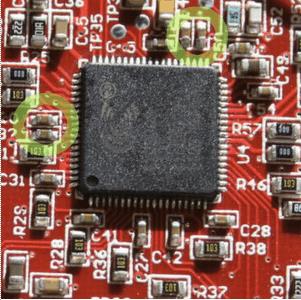

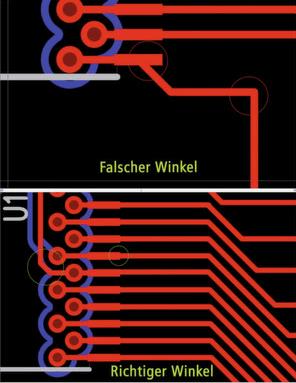

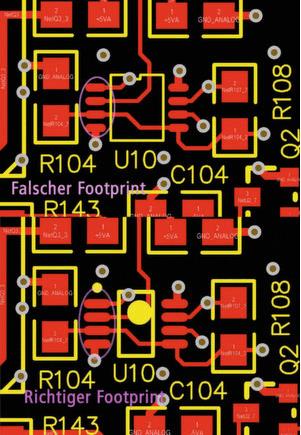

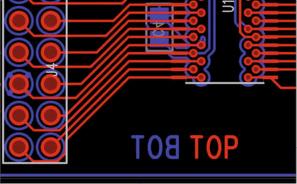

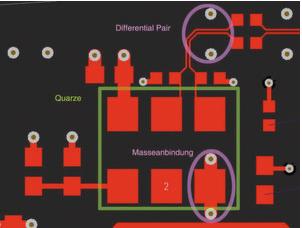

Die 7. Sünden beim Leiterplatten-Design12.03.12 | Autor / Redakteur: Natalia Bahancova * / Gerd Kucera Bild 1Abblock-SMD-Kondensatoren im PCB-Design Es gibt keinen festgeschriebenen Weg wie Bauteile zu platzieren und deren Verbindungen zu entflechten sind. Aber es gibt PCB-Design-Regeln. Der Beitrag skizziert sieben gravierende Regelverstöße beim Leiterplatten-Design. Eine kleine Besonderheit worauf Sie achten sollten gleich zu Beginn: Wenn Sie sich ein Leiterplatten-Layout in einem EDA-Tool wie Altium Designer anschauen, wird Ihnen viel verkehrt herum geschriebener Text auffallen. Sind Leiterplatten-Layouter alle kleine Mozarts, die gerne mit ihrer Fähigkeit prahlen, spiegelverkehrt schreiben zu können? Nicht ganz: Beim Layouten einer Leiterplatte schauen Sie immer von oben auf die Leiterplatte und durch alle Lagen hindurch, als wären sie transparent. So funktionieren alle Layout-Systeme. Höchstens aus Fertigungs- oder Testgründen werden Sie sich Ihre Leiterplatte von unten anschauen. Diese Durchblick-Methode führt dazu, dass Sie sich daran gewöhnen müssen, Text für die Unterseite gespiegelt zu sehen. Wir werden später noch sehen, warum das wichtig ist. Die Bauteil- und Netzliste liefert der Entwickler, der den Stromlaufplan der Schaltung entwirft. Mechanische Zwänge geben den Umriss und die Sperrflächen vor. Die eigentliche Arbeit des PCB-Designers beginnt also beim Platzieren der Bauteile. Dafür entwickelt jeder Leiterplatten-Designer seine eigene Methode. Sünde 1: Die falsche Lage der Puffer-/Abblock-Kondensatoren

Es gibt keinen absolut richtigen Weg, um Bauteile zu platzieren oder die Verbindungen zu routen, aber es gibt Regeln, die man beachten muss.

|

Basteln > PCB-Service >